Name: Akhil Singh

Project Name: Integrated Bit Error Ratio Tester

Project Overview

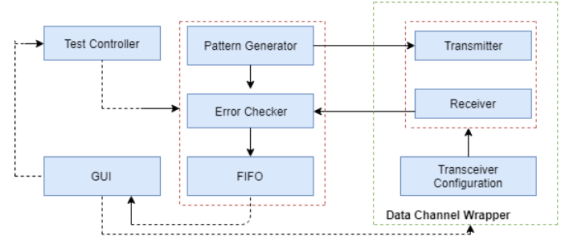

The aim of this project is to create a “Integrated Bit Error Ratio Tester” (iBERT). This project has three parts:

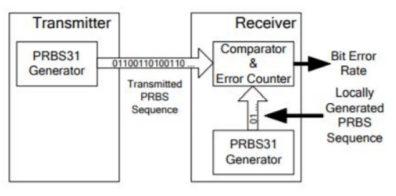

- Data sequence generators + checkers. These generate given bit data stream, then after transmission and receiving check that the bit data stream is correct.

- Data channel wrappers. These give you a common interface to controlling the parameters of a channel used in transmission and receiving.

- Host computer Control GUI / Console. This gives a nice interface for controlling all the parameters and seeing the results of various tests.

All these modules were implemented from scratch and connected together. The functioning of all modules has been verified. All the work done can be found here : https://github.com/akhil-123/Integrated-Bit-Error-Ratio-Tester .

Project Benefits

The major benefits out of this project includes:

- Better testing, since strong test suite has been made to check the combined module as well as individual modules.

- Better documentation, so people can understand what the code is doing.

- Able to use open source tools for simulation, verification and synthesis.

- iverilog for simulation

- yosys for synthesis

- A GUI tool which gives the user a nice interface to examine error rates using different settings.

- For those who want to contribute to this project and have knowledge of verilog can easily contribute.

Original Vs Achieved Goals

- A Fully functional IBERT.

- All the modules which were required for the Integrated Bit Error Ratio Tester have been implemented from scratch.

- Test suite for IBERT.

- The test benches for each of the individual modules have been made to check the working over the individual module and one test bench that will check the working of all the modules at once.

- The GUI has been designed which gives a nice interface to control the different parameters.

- A Benchmark for the comparison of performance.

- This needs to be done.

- Detailed Documentation of the Project.

- Proper documentation of each of the module has been done inside the code and apart from that the top-level design and the overall working documentation is given below.

Work done during GSOC period

The major work which is been done during the GSOC period :

- Build different modules by using verilog. This includes:

- Pattern Generator Module:

- Error Adder Module

- Error checker Module

- Data Channel Wrapper Module

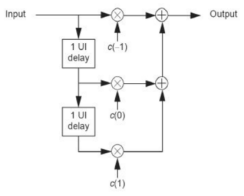

- Pre-emphasis Module

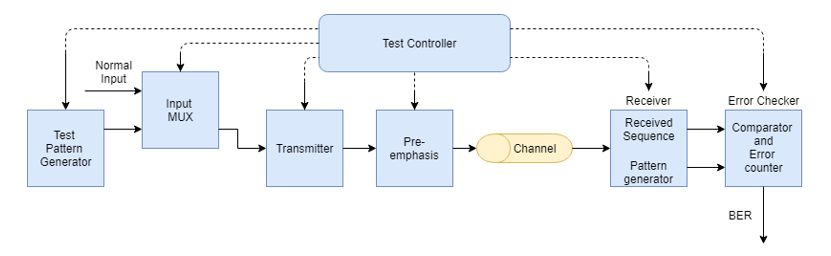

- Test Controller Module

- Build different Test benches for each module to check the functionality of the individual module working. In order to run the test bench, you need to have iverilog installed. After installing iverilog type following commands:

- iverilog -o simple.vvp module1.v module2.v testbench_for_top_module.v

- vvp simple.vvp

- For Example: To run test bench for combined module download files from here and type following commands:

- iverilog -o simple.vvp transmit.v mux.v error.v comp.v DFF.v seven.v thirteen.v choose.v preemph.v test_control.v DCW.v combined.v final_testbench.v

- vvp simple.vvp

- You can see the signal level output for debugging purposes by uncommenting lines 42 and 43 of final_testbench.v and type command:

- gtkwave sim.vcd

- GUI.

- In this link, files ending with extensions html, css, php, js, gif, back are for the GUI.

- Languages used in making the GUI are HTML, CSS, PHP, JS, ajax.

- The project files for different board like zedboard, Cmod A7 t15 and Cmod A7 t35 have been made. The files can be seen here.

- Necessary Documentation for the IBERT.

- The documentation regarding the working of each module is been given inside the code of that module itself and the documentation regarding the top-level design has been given in the documentation section below.

Project Outcome

This project gives the following outcomes:

- Contains all the modules required for the IBERT written in the Verilog language. All modules are connected such that either PRBS-7 or PRBS-13 are selected, then test controller sends control signals to perform pre-emphasis to it and then patterns are transmitted and error is added. At the receiver side test controller sends control signals to do error checking and report the BER. Additionally, test controller can change the input type and can reset the channel.

- Contains a Strong Test Suite in order to check the functionality of the individual module as well as combined module.

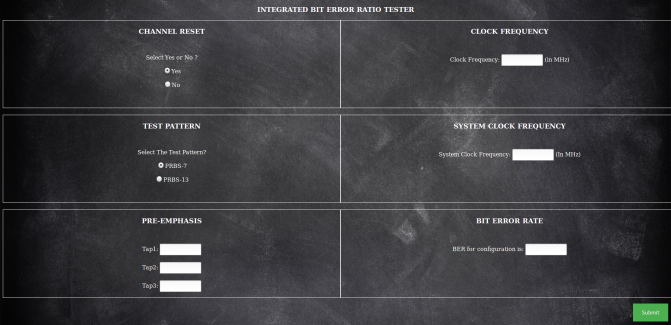

- The GUI has been created which gives a nice interface to control the different parameters and enables the user to see the BER. Options which user can select on GUI are:

- Channel Reset

- Selecting the test patterns

- Tap values for pre emphasis

- Clock frequency (reference clock)

- System clock frequency

How to Replicate Results

In order to make the codes work, following steps needs to be followed:

- If you haven’t php and apache installed on your machine, follow this link to install.

- If you haven’t iverilog installed in your machine, type command:

- sudo apt-get install iverilog

- Cloning this repository IBERT.

- Copy the files to /var/www/html

- cd /var/www/html

- Type command to grant permission :

- “ sudo chmod -R 777 . ”

- Now open the browser and type localhost/home.html

- Now set the parameters that you want and click on submit button.

- On clicking the button you can see the BER as output.

- Apart from this if you want to synthesize the codes, follow this link to install yosys, after installing yosys type command on terminal :

- cd /var/www/html

- yosys synth.ys

Further Contributions to the Project

The following things can be done in the future related to the project:

- Adding functionality in the GUI to dump the codes to fpga from the GUI as currently GUI supports simulation and synthesis.

- Make a platform to compare the performance of the IBERT implemented with the one made by Xilinx (LogiCORE).

DOCUMENTATION

- IBERT Top level design

- Test Controller:

- Pre emphasis:

- Error Checker:

- GUI webpage:

- Link to the code

- Some Important Links:

- GSOC proposal.

- GSOC blog for Daily and Weekly progress.

- Commits.

Learning

Doing this project is a lot fun with a lot of things to learn. The number of such things is more than I can even write but summing up all this the major things which I learn includes:

- Handling large code bases, this was the first time that I written just a large amount of code.

- Putting your doubts in front of others as during this period a number of errors will come and you should have to convey what you want to say to others, seems easy but not that for me at least.

- Importance of indentation and documentation as during this period I refer to some of the other works and at that time the proper documentation and indentation seems a lot of help to me.

Conclusion

A lot of learning has been made during this period. As I want to thank to TimVideos for selecting me. Also I want to thank GSOC team for providing such a platform to introduce to the open source.

Contact details

If you have any doubts or suggestions, you can contact me anytime you want. Here are the details:

Email address: 1997singhakhil@gmail.com

GitHub: akhil-123

Facebook: Akhil Singh

IRC Nickname: akhil_singh